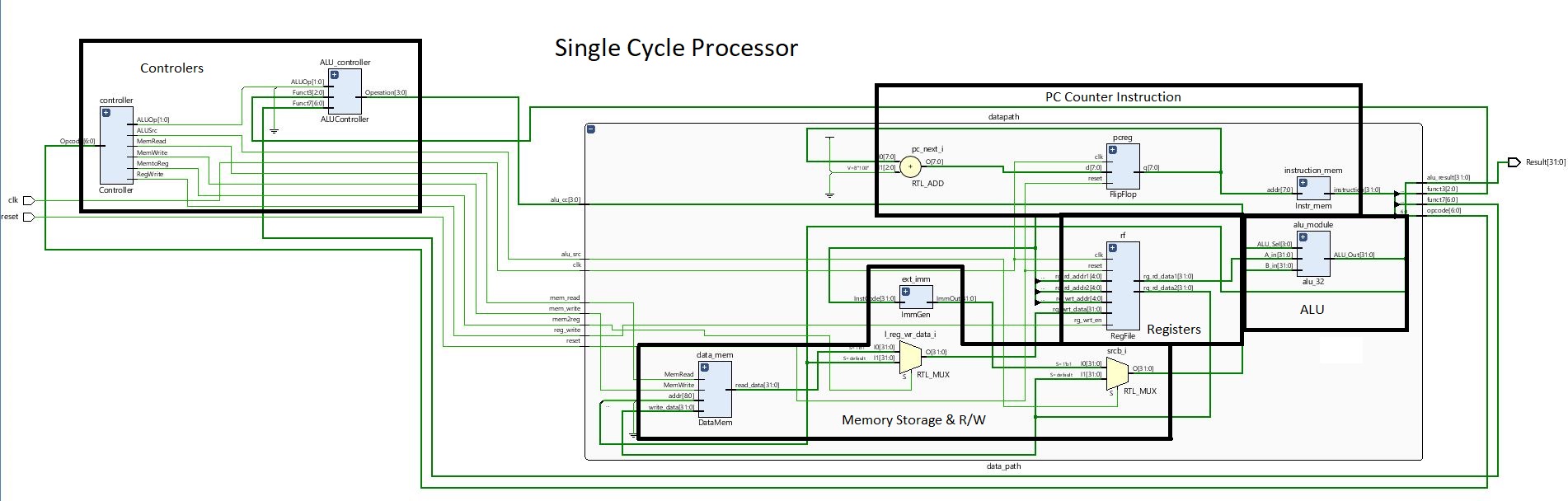

Single Cycle Processor

Description

Single cycle processor that can run simple mips commands. The processor is implemented by 6 parts: Pc counter/instruction Memory, Registers,

ALU, Data Memory, and control module. The pc counter/ Instuction Memory simply stores memory and keeps track of the current instruction.

The registers are the mips registers, simply an array of registers. The ALU implements the basic functions, such as load, store, add etc.

The Data memory is the final memory stored used when user Loads. The control module manages different Instruction types, I type, R type, J type.

The control module required a Karnaugh map to provide efficent parsing of the instruction type.

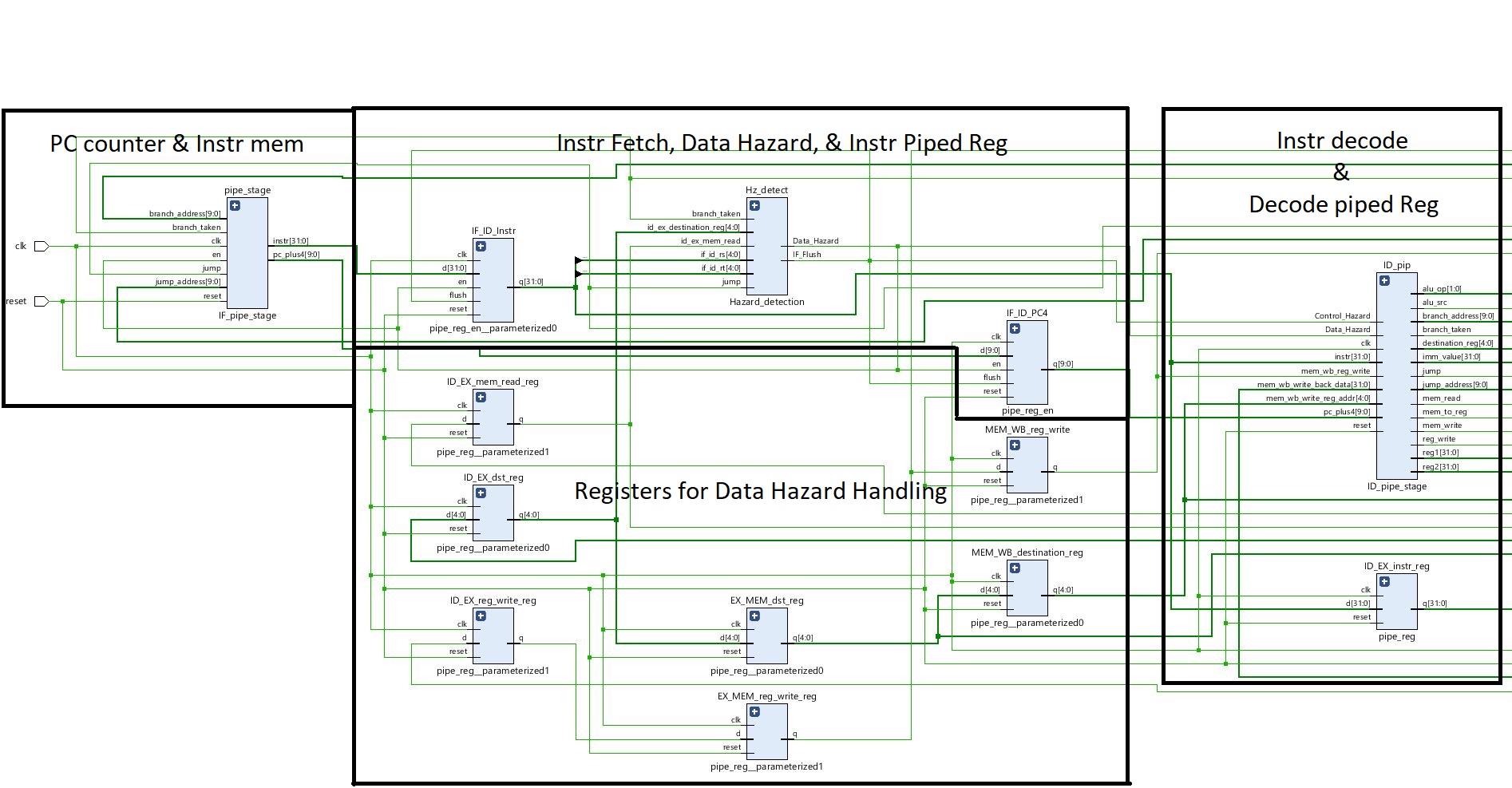

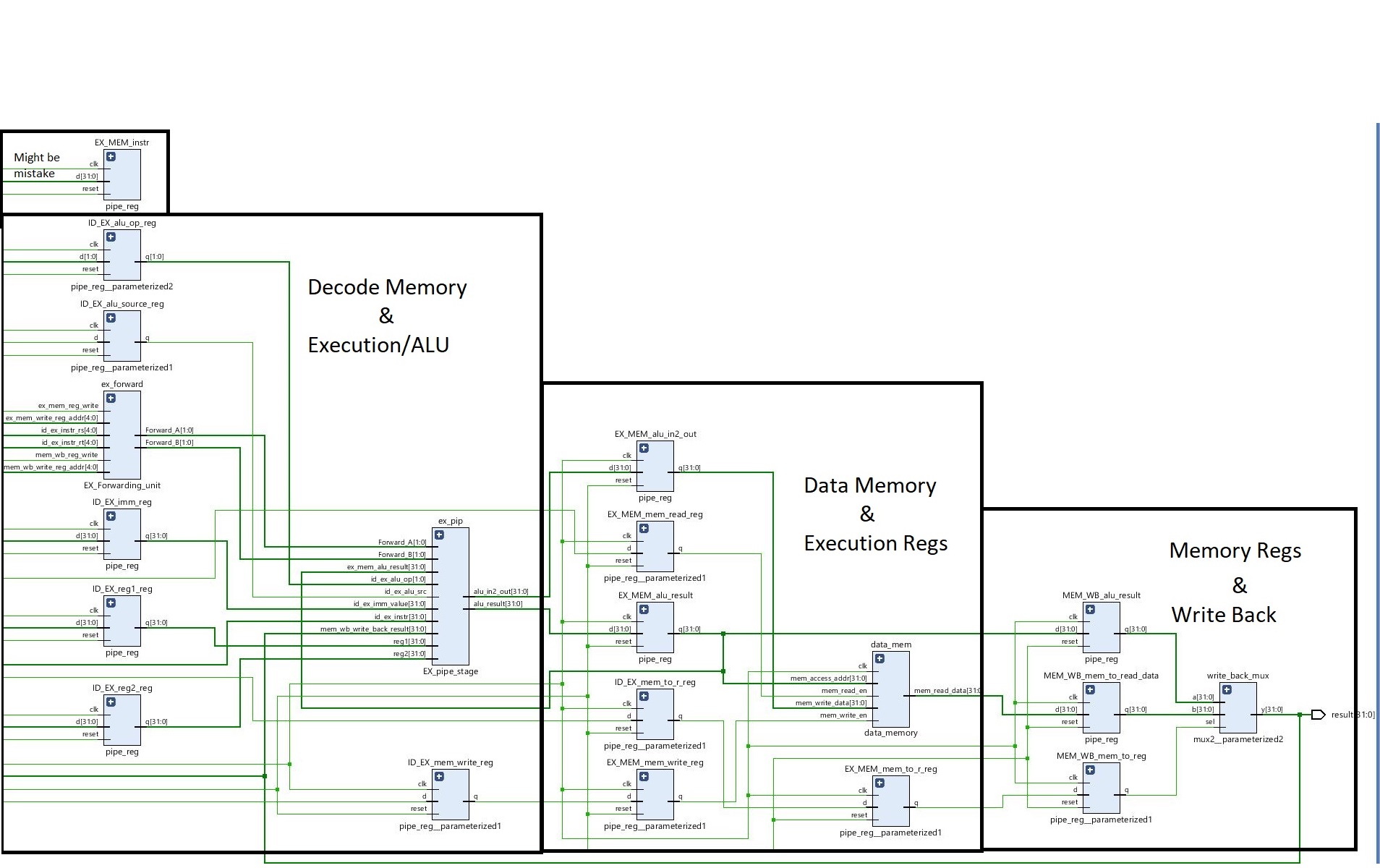

Pipeline Processor

Description

Piped cycle processor that can run simple mips commands. The processor is implemented by 7 parts plus inbetween registers: Pc counter/instruction Memory, Registers,

ALU, Data Memory, control module, and Hazard handler. The processor uses the same logic as the single cycle processor, but provides a register in between

stages to allow for pipeline. The pipline saves registers need and provides them for the next instruction. This cuts the processing time to the longest path each pipe.

The main issues that arises is the hazards that is created by the pipeline, hence the need for a hazard handler module. The hazard check the next instruction and compares

the instruction in the memory stage to see if it causes a hazard. The hazard will produce a NOP if hazard is detected.